ST系列dsPIC33CK

產品描述

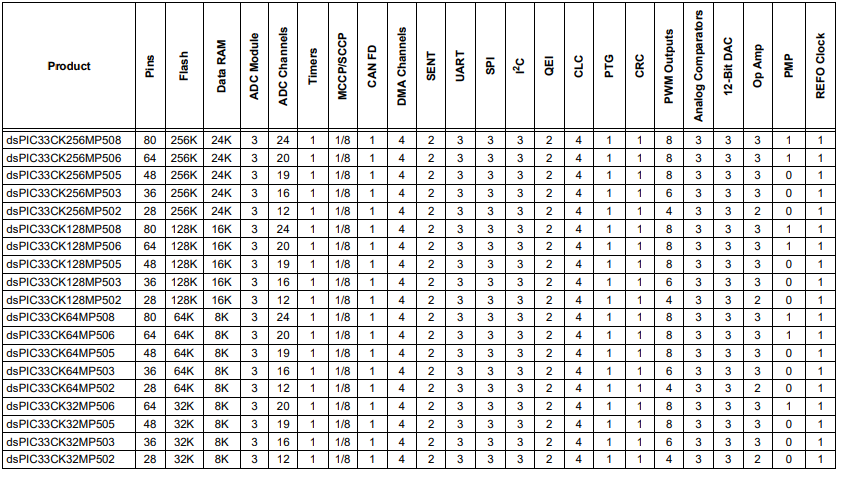

ST系列dsPIC33CK256MP508 FAMILY

操作條件

•3.0V至3.6V,-40°C至+125°C,直流至100 MIPS

•3.0V至3.6V,-40°C至+150°C,直流至70 MIPS

核心:16位dsPIC33CK CPU

•32-256 KB的程序閃存,帶ECC和

8-24K內存

•快速6周除法

•實時更新

•代碼高效(C和彙編)體系結構

•40位寬的累加器

•單週期(MAC/MPY)和雙數據提取

•單循環、混合符號MUL Plus

硬件劃分

•32位乘法支持

•四組中斷上下文保存寄存器

其中包括用於Fast的累加器和狀態

中斷處理

•零開銷循環

•RAM內存內置自檢(MBIST)

時鐘管理

•內部振盪器

•可編程PLL和振盪器時鐘源

•參考時鐘輸出

•故障安全時鐘監視器(FSCM)

•快速喚醒和啟動

•備用內部振盪器

帶CAN FD的dsPIC33CK256MP508系列

主清除(MCLR)引腳MCLR引腳提供兩個特定的設備功能:

•設備重置

•設備編程和調試。

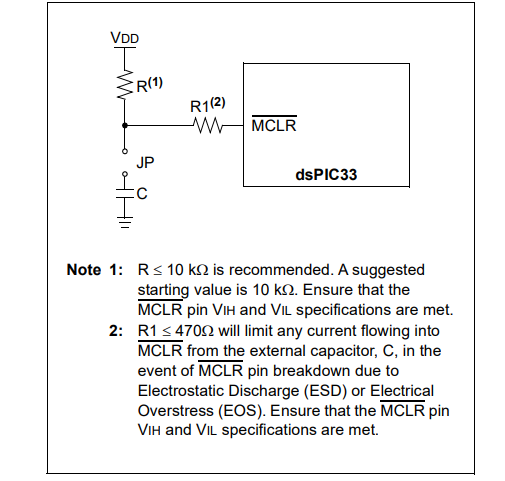

在設備編程和調試期間可添加到電路中的電阻和電容必須考慮銷。設備程序員和調試器驅動MCLR引腳。因此,,特定電壓電平(VIH和VIL)和快速信號過渡不得受到不利影響。所以,,需要調整R和C的具體值基於應用和PCB要求。例如,如圖2-2所示,它是建議將電容器C與電源隔離編程和調試過程中的MCLR引腳操作。放置部件,如圖2-2所示,距離MCLR銷四分之一英吋(6 mm)以內。

圖2-2:MCLR引腳示例

連接2.4 ICSP引腳PGCx和PGDx引腳用於ICSP和調試目的。建議保持ICSP連接器和ICSP之間的記錄道長度設備上的引腳盡可能短。如果ICSP連接器預計會發生ESD事件,則建議使用串聯電阻器,其值在几十歐姆的範圍,不超過100歐姆。上拉電阻器、串聯二極管和電容器不建議使用PGCx和PGDx引腳,因為它們將干擾程序員/調試器與設備的通信。如果這些離散組件如果是應用程序要求,則應刪除它們在編程和調試過程中從電路中分離。或者,參考AC/DC特性和在相應的設備閃存編程信息規範電容性負載限制和引腳電壓輸入過高(VIH)和電壓輸入低(VIL)要求。確保“通信信道選擇”(即。,PGCx/PGDx引腳)編程到設備中將ICSP的物理連接與程序員/調試器。

2.5外部振盪器引腳,當主振盪器(POSC)電路用於連接晶體振盪器,需要特別小心和考慮,以確保正常運行。這個POSC電路應在最終產品預期的環境條件下進行測試被使用。晶體中規定的負載電容器振盪器數據表可用作起點,但是,來自PCB的寄生電容記錄道可能會影響電路,並且這些值可能需要進行更改,以確保正確啟動和運行。過大的跡線長度和其他物理相互作用可能導致信號質量差。調諧不良的振盪器電路可能振幅減小,但不正確頻率(短脈衝)、畸變波形和長脈衝啟動時間可能導致不可預測的應用行為,如指令執行錯誤、非法操作碼提取等。確保晶體振盪器之前,電路處於全振幅和正確頻率系統開始執行代碼。在規劃應用程序的路由和I/O分配,請確保相鄰端口插腳,以及鄰近的其他信號對振盪器沒有高頻,短路上升和下降時間以及其他類似噪音。進一步有關主振盪器的信息,請參見第9.4節“主振盪器(POSC)”

如您要採購ST產品,請聯繫ST官網代理。

如您需要了解更多ST新聞,參考:https://stelectronics.diytrade.com/sdp/2969885/2/nl-7818762/0/ST新聞.html

付款方式︰ TT

產品圖片